# **ICs for Communications**

Smart Integrated Digital Echo Canceller SIDEC

PEB 20954 Version 1.1

Preliminary Data Sheet Apr.1999

| PEB 20954                        |                                 |                                                           |

|----------------------------------|---------------------------------|-----------------------------------------------------------|

| Revision History:                |                                 | Current Version: Apr.1999, Version 1.1                    |

| Page<br>(in previous<br>Version) | Page<br>(in current<br>Version) | Subjects (major changes since last revision)              |

| 7                                | 7                               | power dissipation is 700-900 mW instead of 1200 mW        |

| 7,119                            | 7,122                           | temperature range -40°C - 85°C instead of 0°C - 70°C      |

| -                                | 10                              | section about SIDEC in VoIP added                         |

| 58,60                            | 60,62                           | μP max. timing changed from 20 ns to 25 ns                |

| 101                              | 104                             | Description of bit AACSC.ACSEFFECT corrected              |

| 113,114                          | 116,117                         | Fig. 38 and Fig. 39 interchanged (Now Fig 39 and Fig. 40) |

| 120                              | 123,124                         | AC Characteristics added                                  |

| 121                              | 124                             | Capacitances added                                        |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

ABM®, AOP®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4μC, SLICOFI® are registered trademarks of Infineon Technologies AG.

ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of Infineon Technologies AG.

#### **Edition Apr.1999**

Published by Infineon Technologies AG i. Gr., SC, Balanstraße 73, 81541 München

© Infineon Technologies AG i.Gr. 1999.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| 1<br>1.1<br>1.2<br>1.3                                                                                                        | Introduction  Key Features  Logic Symbol  Typical Applications                                                                                                                                                                                                                                                                                                                                                                                                                   | 6<br>8                                             |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2<br>2.1<br>2.2                                                                                                               | Pin Descriptions          Pin Diagram          Pin Definitions and Functions                                                                                                                                                                                                                                                                                                                                                                                                     | 13                                                 |

| 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>3.1.9<br>3.1.10                  | Functional Description  Functional Block Diagram and Description  Speech Control  Disabling Logic  Adaptive Echo Estimation Unit  PCM Input/Output Interface  Subtractor  Non Linear Processor  Microprocessor Interface  Universal Control and Communication Interface  Watchdog Timer  Clock Control  JTAG and RAM BIST  Test                                                                                                                                                  | 24<br>24<br>25<br>25<br>26<br>26<br>26<br>27<br>27 |

| 3.2<br>3.2.1<br>3.2.2<br>3.2.3                                                                                                | Description of Functional Features  Channelwise and Global A- and μ-Law Conversion  Bypass and Disabling Functions  UCC Interface                                                                                                                                                                                                                                                                                                                                                | 27<br>27<br>29                                     |

| 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8<br>4.3.8.1<br>4.3.8.2<br>4.3.9 | Operational Description Pin Connection Diagram for SIDEC Synchronization and Clock Modes Timing Patterns Clock Timing PCM Signal Timing and Frame Alignment Timing of SYNCI and SYNCO Clock Timing within External VCO Capture Range Serial Interface (Controlling and Monitoring) Timing UCC Interface Signal Timing and Frame Alignment Speech Highway Control Signals for CAS in T1 Systems Microprocessor Interface Intel Mode (IM0='0') Motorola Mode (IM0='1') JTAG Timing | 32<br>33<br>39<br>41<br>46<br>47<br>49<br>53<br>54 |

| 5                                                                                                                             | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65                                                 |

| 5.1   | Register Model                                                                                                                  |

|-------|---------------------------------------------------------------------------------------------------------------------------------|

| 5.2   | Detailed Register Description65                                                                                                 |

| 5.2.1 | Register Map                                                                                                                    |

| 5.2.2 | Read-Write-Register71                                                                                                           |

| 5.2.3 | Write Register72                                                                                                                |

| 5.2.4 | Read Register                                                                                                                   |

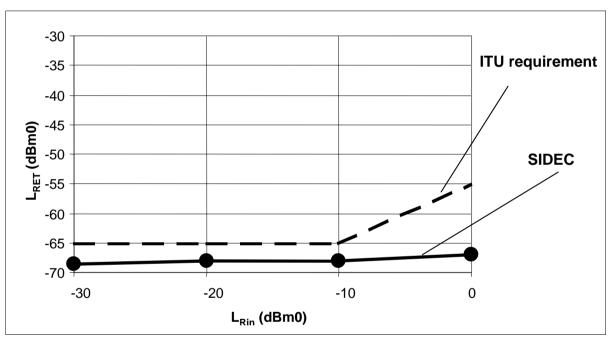

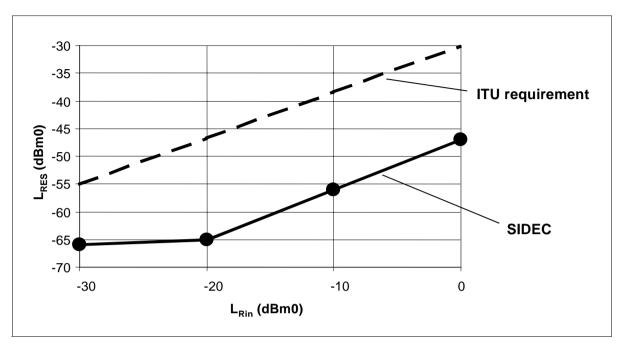

| 6     | SIDEC Performance                                                                                                               |

| 6.1   | Test No.1 - Steady state residual and returned echo level test                                                                  |

| 6.2   | Test No. 2 - Convergence and steady state residual and returned echo level test 118                                             |

| 6.2.1 | Test 2A: Convergence test with NLP enabled                                                                                      |

| 6.2.2 | Test 2B: Convergence test with NLP disabled118                                                                                  |

| 6.2.3 | Test 2C: Convergence test in the presence of background noise 118                                                               |

| 6.3   | Test No. 3 - Performance under conditions of double talk119                                                                     |

| 6.3.1 | Test 3A: Double talk test with low near end levels119                                                                           |

| 6.3.2 | Test 3B: Double talk test with high near end levels                                                                             |

| 6.3.3 | Test 3C: Double talk under simulated conversion                                                                                 |

| 6.4   | Test No. 4 - Leak rate test                                                                                                     |

| 6.5   | Infinite return loss convergence test120                                                                                        |

| 6.6   | Non divergence on narrow band signals120                                                                                        |

| 6.7   | Stability Test120                                                                                                               |

| 6.8   | Test No. 8 - Non convergence of the canceller on specific ITU-T No. 5, 6 and 7 in band signaling and continuity check tones 120 |

| 6.9   | Test No. 9 - Comfort noise test121                                                                                              |

| 6.10  | Test No. 10 - Canceller operation on the calling/caller station side 121                                                        |

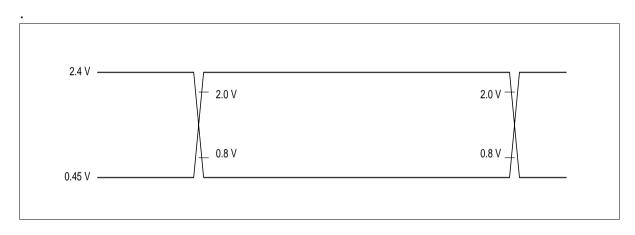

| 7     | Electrical Characteristics122                                                                                                   |

| 7.1   | Absolute Maximum Ratings                                                                                                        |

| 7.2   | Operating Range122                                                                                                              |

| 7.3   | DC Characteristics                                                                                                              |

| 7.4   | AC Characteristics                                                                                                              |

| 7.5   | Capacitances                                                                                                                    |

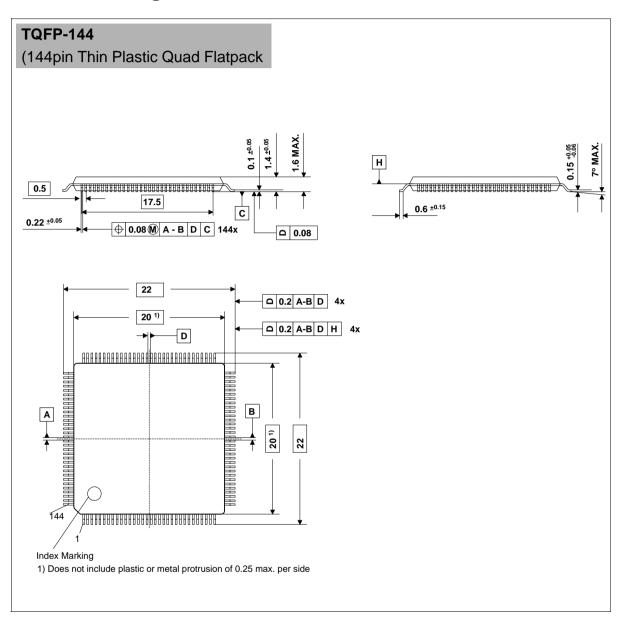

| 8     | Package Outlines                                                                                                                |

| 9     | <b>Glossary</b>                                                                                                                 |

| 10    | Index 131                                                                                                                       |

#### 1 Introduction

The **S**mart Integrated **D**igital **E**cho **C**anceller (SIDEC) suppresses echoes in telecommunication networks which might disturb any kind of terrestrial or wireless communication. It incorporates leading edge CMOS technology as well as SIEMENS' many years' experience in Telecommunication ICs.

In communication links reflections resulting in an electrical echo are due to hybrid splits or imperfect terminations in subscriber loops. Acoustical echoes may occur due to poor isolation of microphone and speaker of some telephone system. These electrical and acoustical echoes disturb the quality of the transmission. To ensure high quality, pure data transmission the ITU-T (International Telecommunications Union, Telecommunication Standardization Sector) suggests in the recommendation G.131 the use of echo cancellers. Echo cancellation is extremely desirable for data links with total round trip transmission times of more than 50 ms.

# Smart Integrated Digital Echo Canceller SIDEC

**PEB 20954**

Version 1.1 CMOS

## 1.1 Key Features

- 2.048 MHz PCM input and output interfaces with selectable μ- and A-Law coding according to ITU G.711

- Rapid convergence of patented algorithm at the beginning or during a connection even in the presence of background noise at the near end subscriber

- Echo return loss enhancement of > 30 dB (ERLE)

- Detection of double talk for adaptive convergence control

- Independently controlled voiceband echo cancelling according to ITU G.165 and G.168 for

- 32 channels with end echo path delay of less than 63.75 ms

- 16 channels with end echo path delay of less than 127.75 ms (usage of two SIDEC in parallel for simultaneous processing of 32 channels is easily possible)

- Smart Non Linear Processor controlled by echoloss, echo path delay and background noise

- Various options for comfort noise injection

- Maskable disabling functions

- 2100 Hz tone with phase reversal detection

- 2100 Hz tone without phase reversal detection

- 2010 Hz continuity check (SS7)

- via PCM timeslot 16 Bit a, b, c or d according to ITU G.704

- individual channels maskable via Microprocessor Interface, UCC Interface and Serial Interface

- Integrated Universal Control and Communication Interface (UCCI) for signaling highways with direct hardware control for:

- disable cancelling

- configurable disabling functions

- communication between board controllers

| Туре      | Package  |

|-----------|----------|

| PEB 20954 | TQFP-144 |

- Support of Channel Associated Signaling (CAS) BR transparency (robbed bits) in send path

- Selectable μ- to A-Law or A- to μ-Law Conversion on a global or per channel basis

- Configurable idle channel supervision

- Clear channel capability (64 clear) on a per channel basis

- Special evaluation of bit 8 in T1 Modem calls possible (56 clear)

- Serial 256 kbit/s interface to control the functions disable cancelling, freeze coefficients, clear channel, disable NLP, PCM Law conversion control or combinations of above

- Monitor pins for several internal states

- Switchable global loop from receive output to send input and send output to receive input

- Switchable global attenuation (2.5 dB or 6 dB) at the receive and send output

- Flexible Microprocessor Interface (SIEMENS/Intel or Motorola type, Mux and Demux mode) usable for:

- configuration of parameters such as thresholds and functions on a global basis

- Disable cancelling, freeze coefficients, clear channel, disable NLP, PCM Law conversion control (all functions individually for each channel)

- support of background tests for disabled or idle timeslots (feeding and reading of test levels)

- possibility to read levels, attenuations, internal states, signal values or all coefficients of a selected timeslot

- control of the RAM Built In Self Test

- Advanced Integrated Watchdog Timer

- Supervision of the input clocks

- Various clock modes possible for 32.768 MHz and 8.192 MHz

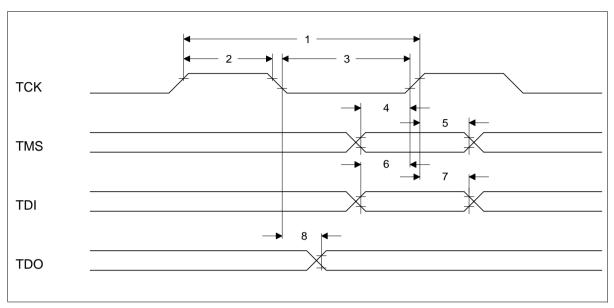

- Boundary Scan according to IEEE 1149.1 Standard

- Power supply: 3.3 V, 5V tolerant inputs

- Typical power dissipation: 700 900 mW

- Plastic package TQFP 144

- Temperature range: -40°C 85°C

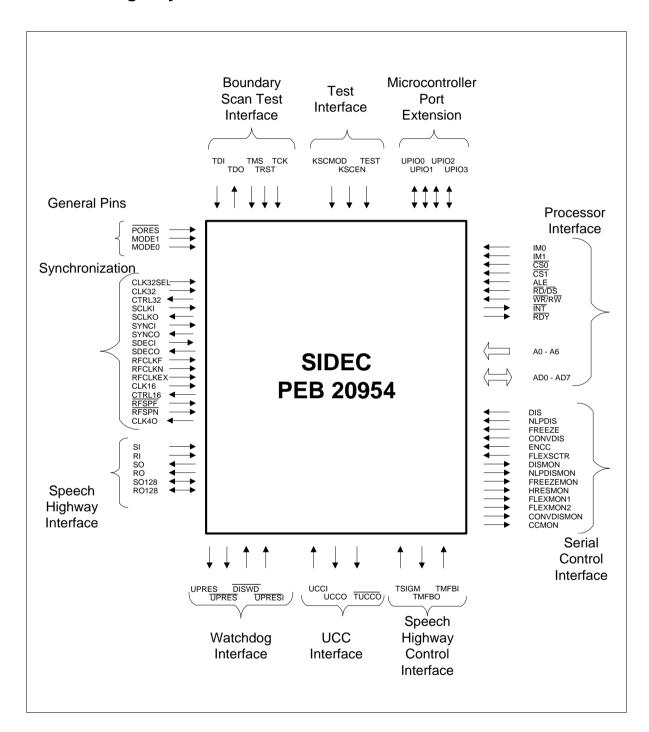

## 1.2 Logic Symbol

Figure 1 Logic Symbol of the SIDEC

## 1.3 Typical Applications

The SIDEC can be used for various applications.

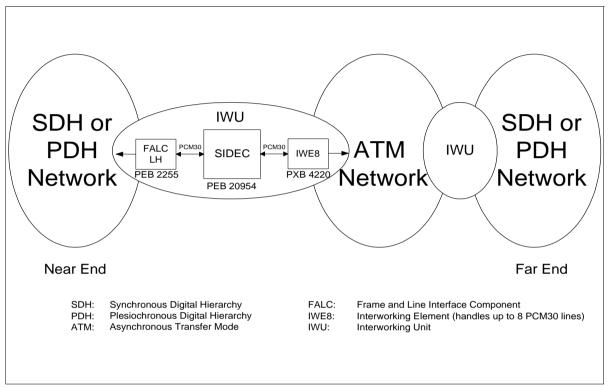

Figure 2 to Figure 5 display typical examples.

Figure 2 SIDEC in a Circuit Emulation Service Carried over ATM

In this interworking unit there are two SIEMENS products connected to the SIDEC. The FALC PEB 2255 serves as a frame and line interface component whereas the IWE8 PXB 4220 operates as an interworking element.

The delays of networks and the inter working units are usually long. In the application above the SIDEC cancels the echo that is generated by reflection on the near end side and heard by the far end speaker. The SIDEC can cancel end echo paths (SDH or PDH Network on near end side) up to 128 ms. For details see **Figure 11**.

For the set up illustrated in **Figure 2** a application note "Using SIDEC in a Voice over ATM Application" is available.

9

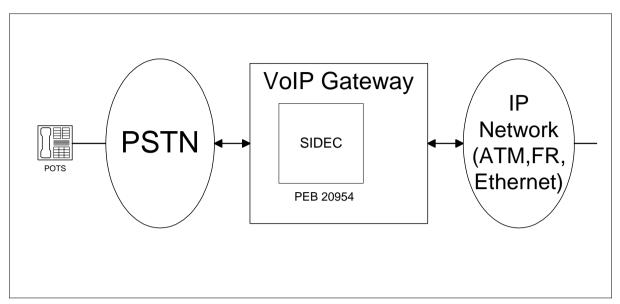

Figure 3 SIDEC in a Voice over IP Gateway

An emerging market in the telecom industry is "Voice Over IP". Due to the long delay echo cancellation is required. The delay is introduced through packetizing and voice compression. The SIDEC handles different functions in a Voice over IP gateway, such as Voice Detection, Voice Activity Detection, Comfort Noise and A-law u-law conversion regarding G.711.

In a gateway the SIDEC points into the PSTN network as shown in **Figure 3**. The echo itself is generated by the hybrid in the PSTN cloud. Before the voice signal from the POTS gets packetized into ATM, FR or Ethernet cells the echo is being cancelled by the SIDEC.

For a high voice quality in "Voice Over IP" environment echo cancellation is a major requirement.

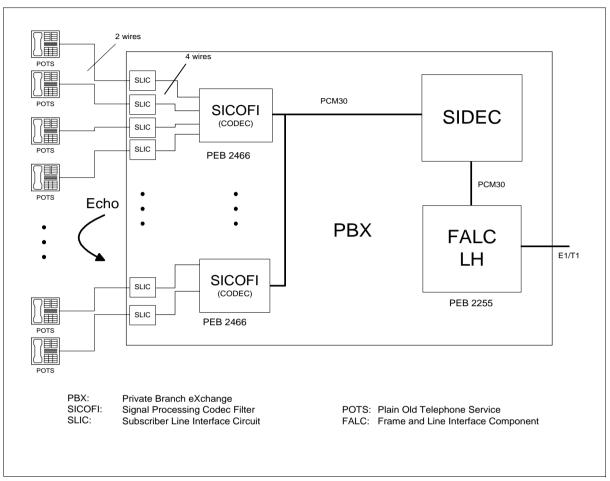

Figure 4 SIDEC in a Private Branch Exchange (PBX)

SIDEC can be used in a PBX or Central Office (CO) to cancel the echo next to the customer side (near end echo). The echo delay is kept short. The delay for this application is usually less than 64ms and the SIDEC can cancel up to 32 channels.

**Figure 4** shows a PBX with a T1/E1 interface FALC LH to the CO on the one side. On the other side analog phones are connected.

A possible SIEMENS solution with the SICOFI (includes D/A and A/D conversion) and the SLIC (hybrid) to connect the analog phone is shown above.

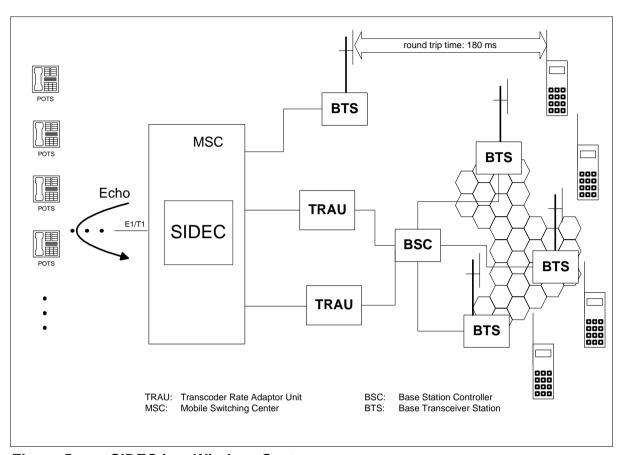

Figure 5 SIDEC in a Wireless System

Due to voice compression and error correction the one way transmission time for wireless voice signals is typically 90 ms. With 180 ms roundtrip time the 50 ms roundtrip time for echo free transmission is exceeded by at least 130 ms. Hence, the speaker on the mobile phone will hear any kind of echo generated in the hybrid next to the POTS or the acoustical echo of the POTS. The SIDEC suppresses those two kinds of echoes if it is incorporated in the MSC. Depending on the individual call the end echo path can differ dramatically. In Europe the end echo path could even go to different countries causing strong dispersion of the echo. Only a high quality echo canceller with long end path delay options guarantees compensation of the strongly varying echoes.

# 2 Pin Descriptions

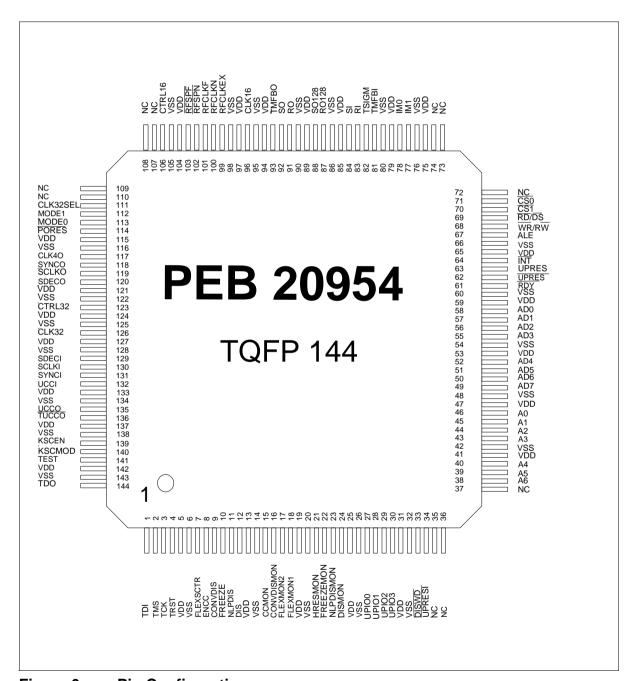

## 2.1 Pin Diagram

Figure 6 Pin Configuration

# 2.2 Pin Definitions and Functions

Table 1 General Pins

| Pin No.    | Symbol         | Input (I) Output (O) Pull Up / Pull Down | Funct | tion                                 |     |                                     |

|------------|----------------|------------------------------------------|-------|--------------------------------------|-----|-------------------------------------|

| 114        | PORES          | I, PU                                    |       | r On Reset. A lovers and counters    |     | •                                   |

| 112<br>113 | MODE1<br>MODE0 | I, PU<br>I, PU                           | 1     | End delay < 64ms                     | 1 0 | For future use                      |

| 112<br>113 | MODE1<br>MODE0 | I, PU<br>I, PU                           | 0     | End delay <<br>128 ms Master<br>Mode | 0   | End delay <<br>128 ms Slave<br>Mode |

Table 2

Synchronization

| Pin No. | Symbol   | I/O, PU/PD | Function                                                                                                                                                       |

|---------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 111     | CLK32SEL | I, PU      | Selects from which source SCLKO will be derived: '1': SCLKO will be derived from CLK32 by dividing by 4 '0': SCLKO will be derived from CLK16 by dividing by 2 |

| 126     | CLK32    | I, PU      | 32.768 MHz Operating Clock for the SIDEC                                                                                                                       |

| 123     | CTRL32   | 0          | Control voltage for the 32.768 MHz operating Clock VCO, maskable for reduced power consumption                                                                 |

| 130     | SCLKI    | I, PU      | System clock input (8.192 MHz) for PCM- and UCCI                                                                                                               |

| 119     | SCLKO    | О          | 8.192 MHz system clock output, source CLK32 or CLK16 is selectable via pin CLK32SEL, maskable for reduced power consumption                                    |

| 117     | CLK4O    | 0          | 4.096 MHz system clock output for subsequent circuits, derived from SCLKI, maskable for reduced power consumption                                              |

| Pin No. | Symbol | I/O, PU/PD | Function                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 131     | SYNCI  | I, PU      | System Synchronization input pulse. Defines the frame alignment of PCM and UCCI signals in conjunction with the values in registers RIALIGN, SIALIGN, SOALIGN, UCCALIGN, PHALIGN and also the multiframe alignment of the UCCI. Must be integer multiple of 125 µs if UCC Interface is not used. Must be multiple integer of 4 ms if UCC interface is used. Leave open if not used or connect to V <sub>DD</sub> |

| 118     | SYNCO  | O          | System Synchronization output pulse (see SYNCI), duration configurable one or two SCLKO periods, period 125 µs. If the UCC interface is not used and no SYNCI is applied, SYNCO can take over the part and role of SYNCI.                                                                                                                                                                                        |

| 120     | SDECO  | 0          | Synchronization output pulse for other SIDECs if this SIDEC uses its own 32.768 MHz VCO. Can also be used for synchronization of external devices to the serial control input and monitor output signals of the SIDEC. The pulse width is 488 ns with a period of 125 µs.                                                                                                                                        |

| 129     | SDECI  | I, PU      | Synchronization input pulse if the SIDEC uses the 32.768 MHz VCO of another SIDEC. The same SCLKI signal can be applied to SDECI and SCLKI pin if the SCLKI is supplied by a source with correct phase condition to the CLK32 (see <b>Figure 14</b> ). If the pin is not used leave it open or connect it to V <sub>DD</sub> .                                                                                   |

| 101     | RFCLKF | I, PU      | Reference clock (2.048 MHz) for frequency comparison to generate the control voltage for the 16.384 MHz VCXO if Register FSLIPIV[6:5]="00"                                                                                                                                                                                                                                                                       |

| 100     | RFCLKN | I, PU      | Reference clock (2.048 MHz) for frequency comparison to generate the control voltage for the 16.384 MHz VCXO if Register FSLIPIV[6:5]="01"                                                                                                                                                                                                                                                                       |

| Pin No. | Symbol  | I/O, PU/PD | Function                                                                                                                                                                                                                                   |

|---------|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 99      | RFCLKEX | I, PU      | Reference clock (2.048 MHz) for frequency comparison to generate the control voltage for the 16.384 MHz VCXO if Register FSLIPIV[6]='1'                                                                                                    |

| 96      | CLK16   | I, PU      | Clock from 16.384 MHz VCXO                                                                                                                                                                                                                 |

| 106     | CTRL16  | 0          | Control voltage for the 16.384 MHz VCXO                                                                                                                                                                                                    |

| 103     | RFSPF   | I, PU      | Receive Frame Sync Pulse from the far end side (F1). This pulse of 488 ns width marks timeslot 0 when writing into Elastic Store (e.g. FALC) to prevent faults in one frame length mode. To use this pin Register FSLIPIV[5] must be '0'.  |

| 102     | RFSPN   | I, PU      | Receive Frame Sync Pulse from the near end side (F2). This pulse of 488 ns width marks timeslot 0 when writing into Elastic Store (e.g. FALC) to prevent faults in one frame length mode. To use this pin Register FSLIPIV[5] must be '1'. |

Table 3 Microprocessor Interface

| Pin No.        | Symbol | I/O, PU/PD | Function                                                                                                                                                                                                                                                                                                                     |

|----------------|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 78             | IMO    | I, PU      | Interface Mode SIEMENS/Intel = low,<br>Motorola = high                                                                                                                                                                                                                                                                       |

| 77             | IM1    | I, PU      | Interface Mode MUXED = low, DEMUXED = high                                                                                                                                                                                                                                                                                   |

| 71             | CS0    | I, PU      | Chip Select. A low signal selects the SIDEC (internally "anded" with $\overline{CS1}$ ).                                                                                                                                                                                                                                     |

| 70             | CS1    | I, PU      | Chip Select. A low signal selects the SIDEC (internally "anded" with $\overline{\text{CSO}}$ ).                                                                                                                                                                                                                              |

| 46-43<br>40-38 | A0A6   | I, PU      | Address Bus. Only used in demuxed mode, can be left open in muxed mode.                                                                                                                                                                                                                                                      |

| 58-55<br>52-49 | AD0AD7 | I/O, -     | Multiplexed Address/Data Bus in multiplexed mode, Data Bus in demultiplexed mode                                                                                                                                                                                                                                             |

| 67             | ALE    | I, PU      | Address Latch Enable in multiplexed mode. Address on AD bus is internally latched with the falling edge of ALE. This signal is also used for the internal clock supervision. In Demuxed mode there must be provided an external independent clock signal (i.e. processor clock) in order to enable proper clock supervision. |

| 69             | RD/DS  | I, PU      | SIEMENS/Intel mode. A low indicates a read operation.  Motorola mode. Data Strobe, active low to control read/write                                                                                                                                                                                                          |

| 68             | WR/RW  | I, PU      | SIEMENS/Intel mode. A low indicates a write operation.  Motorola mode. High = read cycle, low = write cycle                                                                                                                                                                                                                  |

| 64             | ĪNT    | O, (od)    | Interrupt request from the SIDEC, active low                                                                                                                                                                                                                                                                                 |

| 61             | RDY    | O, (od)    | Ready signal for µC devices that support this feature. For read cycles the signal is asserted after the data on the AD bus is valid. For writing cycles the signal is asserted when a write access is ready to be concluded.                                                                                                 |

Table 4 Microcontroller Port Extension

| Pin No. | Symbol | I/O, PU/PD | Function                                                                        |

|---------|--------|------------|---------------------------------------------------------------------------------|

| 27      | UPIO0  | I/O, PU    | Pin that can be read and controlled by the on board processor via register UPIO |

| 28      | UPIO1  | I/O, PU    | Pin that can be read and controlled by the on board processor via register UPIO |

| 29      | UPIO2  | I/O, PU    | Pin that can be read and controlled by the on board processor via register UPIO |

| 30      | UPIO3  | I/O, PU    | Pin that can be read and controlled by the on board processor via register UPIO |

Table 5

Processor Watchdog Circuit

| Pin No. | Symbol | I/O, PU/PD | Function                                                                                                                                                                                 |

|---------|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63      | UPRES  | 0          | μP-Reset. High pulse (125 μs) if the μP fails to write predefined values to the registers WDG1 to WDG3 in this sequence within 2 s and DISWD='1'. Also active if PORES='0' or UPRESI='0' |

| 62      | UPRES  | 0          | Same as UPRES, but low active                                                                                                                                                            |

| 33      | DISWD  | I, PU      | Disable of µP-Reset on active watchdog condition if set to low                                                                                                                           |

| 34      | UPRESI | I, PU      | Produces a reset signal at UPRES, UPRES if set to low                                                                                                                                    |

Table 6 Speech Highways

| Pin No. | Symbol | I/O, PU/PD | Function                                                                                                                                                                               |

|---------|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 84      | SI     | I, PD      | 2.048 Mbit/s Send speech highway input. Start of timeslot 0, bit 7 can be flexibly aligned to the SYNCI/SYNCO pulse in 122 ns steps via registers SIALIGN and PHALIGN[3:2]             |

| 83      | RI     | I, PD      | 2.048 Mbit/s Receive speech highway input.<br>Start of timeslot 0, bit 7 can be flexibly aligned<br>to the SYNCI/SYNCO pulse in 122 ns steps via<br>registers RIALIGN and PHALIGN[1:0] |

| Pin No. | Symbol | I/O, PU/PD | Function                                                                                                                                                                                                                                                                                                                                                                                             |  |

|---------|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 92      | SO     | 0          | 2.048 Mbit/s Send speech highway output.<br>Start of timeslot 0, bit 7 can be flexibly aligned<br>to the SYNCI/SYNCO pulse in 122 ns steps via<br>registers SOALIGN and PHALIGN[5:4]                                                                                                                                                                                                                 |  |

| 91      | RO     | 0          | 2.048 Mbit/s Receive speech highway output. This signal will has a fixed delay of one PCM frame (125 µs) with respect to RI                                                                                                                                                                                                                                                                          |  |

| 88      | SO128  | I/O, PU    | Auxiliary 2.048 Mbit/s Send speech highway output in 128 ms mode. Input in master mode, output in slave mode. The pins of master and slave SIDEC in 128 ms mode should be connected to enable a 32 channel system. The signal from the slave is multiplexed in the master with the internally generated signal and output (clocked) with the system clock. Tristate and meaningless in 64 ms mode    |  |

| 87      | RO128  | I/O, PU    | Auxiliary 2.048 Mbit/s Receive speech highway output in 128 ms mode. Input in master mode, output in slave mode. The pins of master and slave SIDEC in 128 ms mode should be connected to enable a 32 channel system. The signal from the slave is multiplexed in the master with the internally generated signal and output (clocked) with the system clock. Tristate and meaningless in 64 ms mode |  |

Table 7 UCC Interface

| Pin No. | Symbol | I/O, PU/PD | Function                                                                                                                                                                                                                                                                    |

|---------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 132     | UCCI   | I, PD      | 2.048 Mbit/s UCC highway input. Start of timeslot 0, bit 7 and frame number can be flexibly aligned to the SYNCI/SYNCO pulse in 122 ns steps via registers UCCMFR, UCCALIGN and PHALIGN[7:6]                                                                                |

| 135     | UCCO   | 0          | 2.048 Mbit/s UCC highway output. Start of timeslot 0, bit 7 and frame number can be flexibly aligned to the SYNCI/SYNCO pulse in 122 ns steps via registers UCCMFR, UCCALIGN and PHALIGN[7:6]                                                                               |

| 136     | TUCCO  | 0          | Tristate control signal for external tristate output buffer at the UCCO bus, active low. Remains inactive after a power on reset until the configuration by the µP has been settled. Active only at UCC timeslot 0 for UCC frames that correspond to processed PCM channels |

Table 8 Speech Highway Control Signals for Channel Associated Signaling (CAS) in T1 Systems

| Pin No. | Symbol | I/O, PU/PD | Function                                                                                                                             |

|---------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 82      | TSIGM  | I, PD      | Transmit Signaling Marker, indicating robbed bits at SI, corresponding to the delay of SI                                            |

| 81      | TMFBI  | I, PD      | Transmit Multiframe Begin Input corresponding to the delay of SI                                                                     |

| 93      | TMFBO  | 0          | Transmit Multiframe Begin Output corresponding to the delay of SO. The delay of TMFBI to TMFBO is identical to the delay of SI to SO |

Table 9 Channelwise Serial Interface

| Pin No. | Symbol    | I/O, PU/PD | Function                                                                                                                                                                                                                  |

|---------|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12      | DIS       | I, PD      | Serial 256 kbit/s disable signal to bypass the canceller, NLP and attenuator and to reset the H-Register and Speech Control unit on a per channel basis. High active, maskable, leave open or connect to ground if unused |

| 11      | NLPDIS    | I, PD      | Serial 256 kbit/s signal to disable the NLP on<br>a per channel basis. High active, maskable,<br>leave open or connect to ground if unused                                                                                |

| 10      | FREEZE    | I, PD      | Serial 256 kbit/s signal to freeze the H-<br>Registers on a per channel basis. High active,<br>maskable, leave open or connect to ground if<br>unused                                                                     |

| 9       | CONVDIS   | I, PD      | Serial 256 kbit/s signal to disable A/μ-Law conversion on a per channel basis. High active, maskable, leave open or connect to ground if unused                                                                           |

| 8       | ENCC      | I, PD      | Serial 256 kbit/s signal to enable clear channel transparency on a per channel basis. High active, maskable, leave open or connect to ground if unused, same function as DIS='1' and CONVDIS='1'                          |

| 7       | FLEXSCTR  | I, PD      | Flexible serial 256 kbit/s control signal on a per channel basis. Configurable by register CONFLEXSCTR. High active, maskable, leave open or connect to ground if unused                                                  |

| 24      | DISMON    | 0          | Serial 256 kbit/s EC disable (signals bypass channels) monitor output signal ('0': EC on, '1': EC off)                                                                                                                    |

| 23      | NLPDISMON | 0          | Serial 256 kbit/s NLP disable monitor output signal ('0': NLP on, '1': NLP off)                                                                                                                                           |

| 22      | FREEZEMON | 0          | Serial 256 kbit/s H-Register freeze monitor output signal ('1': freeze, '0': no freeze)                                                                                                                                   |

| 21      | HRESMON   | 0          | Serial 256 kbit/s H-Register reset monitor output signal ('1': reset, '0': no reset)                                                                                                                                      |

| Pin No. | Symbol     | I/O, PU/PD | Function                                                                                                                                                                                                                                                                            |

|---------|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18      | FLEXMON1   | 0          | Serial 256 kbit/s monitor output signal (32 channels at 8 kbit/s), monitoring according to settings of the bits CONFLEXMON[7:4], e.g. Idle channel detection, 2010 Hz tone detected, 2100 Hz tone with or without phase reversal detected, double talk detected, no speech detected |

| 17      | FLEXMON2   | 0          | Serial 256 kbit/s monitor output signal (32 channels at 8 kbit/s), monitoring according to settings of the bits CONFLEXMON[3:0], e.g. Idle channel detection, 2010 Hz tone detected, 2100 Hz tone with or without phase reversal detected, double talk detected, no speech detected |

| 16      | CONVDISMON | 0          | Serial 256 kbit/s law conversion disable monitor output signal ('1': conversion disabled, '0': conversion enabled)                                                                                                                                                                  |

| 15      | CCMON      | 0          | Serial 256 kbit/s clear channel transparency (64 clear) monitor output signal ('1': clear channel on, '0': clear channel off), same as DISMON='1' and CONVDISMON='1'                                                                                                                |

Table 10 Test Interface for Boundary Scan according to IEEE 1149.1

| Pin No. | Symbol | I/O, PU/PD | Function                                                                     |  |

|---------|--------|------------|------------------------------------------------------------------------------|--|

| 1       | TDI    | I, PU      | Test Data Input                                                              |  |

| 144     | TDO    | 0          | Test Data Output                                                             |  |

| 2       | TMS    | I, PU      | Test Mode Select                                                             |  |

| 3       | TCK    | I, PU      | Test Clock                                                                   |  |

| 4       | TRST   | I, PU      | Boundary Test Reset (active low, should be tied to '0' for normal operation) |  |

## Table 11 Test Interface

| Pin No. | Symbol | I/O, PU/PD | Function                                                                                                                                                                                               |

|---------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 140     | KSCMOD | I, PD      | SCAN MODE ENABLE pin for enabling of scan test. For normal operation this pin should be left unconnected or connected to V <sub>SS</sub> .                                                             |

| 139     | KSCEN  | I, PD      | SCAN SHIFT ENABLE pin for shift enabling in scan test. For normal operation this pin should be left unconnected or connected to V <sub>SS</sub> .                                                      |

| 141     | TEST   | Ι, -       | Reserved for special tests (i.e. IDDQ, MBIST, etc.). For normal operation this pin must be connected to V <sub>SS</sub> . Disables all pull resistances for IDDQ if set to '1'. Normal operation: '0'. |

# 3 Functional Description

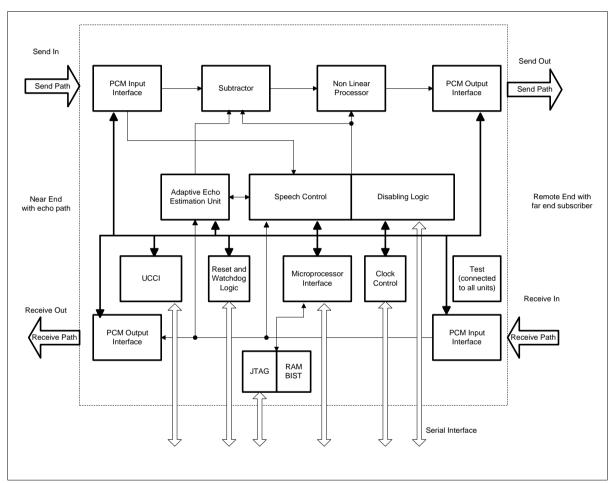

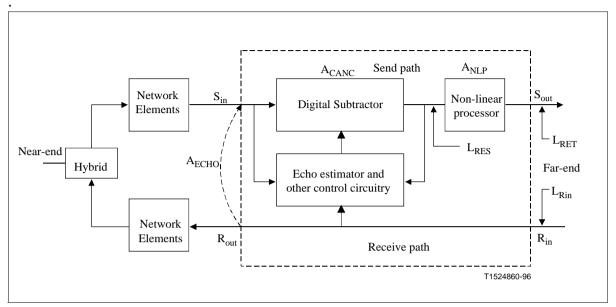

Figure 7 depicts the Functional Block Diagram of the SIDEC.

## 3.1 Functional Block Diagram and Description

Figure 7 Block Diagram

The following paragraphs describe the functions of the SIDEC block diagramm shown in **Figure 7**.

# 3.1.1 Speech Control

The Speech Control analyzes the data from the PCM Input Interfaces and external inputs and supervises the functions of the other system components. As soon as the far end subscriber talks, the Adaptive Echo Estimation Unit is activated by the Speech Control. If the double talk condition is detected or a non speech signal with an adequate echo loss enhancement is identified by the Speech Control, the content of the Adaptive Echo Estimation Unit is frozen. Under specific circumstances a reset of the H-Register

(described in Section **3.1.3**) of the Adaptive Echo Estimation Unit might be necessary. The H-Register reset signal is also provided by the Speech Control.

#### 3.1.2 Disabling Logic

Upon request of the Speech Control and depending on external inputs the Disabling Logic disables the Non Linear Processor and/or the Subtractor or even the complete Echo Canceller.

If the Speech Control Unit detects, that one of the following conditions is applied to the Echo Canceller, it will disable the device via the Disabling Logic:

- Disabling via 2100 Hz tone without phase reversal

- Disabling via 2100 Hz tone with phase reversal

- Disabling via 2010 Hz continuity check

- Disabling via PCM timeslot 16 Bit a, b, c or d according to ITU G. 704

- Disabling via Idle channel detection.

- Disabling of individual channels via external interfaces (μP, serial and/or UCC interface)

### 3.1.3 Adaptive Echo Estimation Unit

The Adaptive Echo Estimation Unit contains for each 8 bit signal sampled at 8 kHz memory for 512 / 1024 byte. This is equivalent to 64 / 128 ms end echo path delay. Depending on the end echo path delay of 64 or 128 ms the Adaptive Echo Estimation Unit processes 32 or 16 channels simultaneously, respectively. The corresponding 32 / 16 H-Register for each channel representing the pulse response of the complete echo path are also stored in the Adaptive Echo Estimation Unit. This information simplifies the detection of double speech. A highly sophisticated and patented algorithm guarantees fast and stable convergence even in the presence of near end speech.

The Adaptive Echo Estimation Unit is connected to the Microprocessor Interface in order to configure parameters of the algorithm and to read the content of the H-Register.

# 3.1.4 PCM Input/Output Interface

Each PCM Input/Output Interface contains a delay element, that is adjustable for max 125  $\mu$ s delay in 122 ns steps in order to align the corresponding PCM signal to the synchronizing pulse. Unless not bypassed, the delay from Receive In to Receive Out is fixed to one PCM Frame equivalent to 125  $\mu$ s. The signal Multiframe Begin is delayed accordingly to the send path delay.

Encoder to convert A- or  $\mu$ -Law PCM signals to linear, and decoder to convert linear PCM signals to A- or  $\mu$ -Law allow for channelwise Law Conversion (transcoding).

Offset adjustment is implemented at the output of the canceller. The attenuation of 0 dB, 2.5 dB or 6 dB is programmable by a register. The use of this feature requires that the cancelling function for the corresponding timeslot is enabled.

The complete bypassing of individual timeslots and connections from and to the processor interface with the internal canceller is provided for testing of cancelling timeslots.

The least significant bit in the send path can be transmitted transparently to the output if the corresponding external pin TSIGM is activated (CAS bit robbing).

The block PCM Input/Output Interface provides time multiplexing/demultiplexing for 16 or 32 timeslots. (depending on configuration, see section above). In 128 ms echo end path mode the selection of timeslots at the input is assigned as follows:

| <ul> <li>Master: Timeslot</li> </ul> | 0,1,2,3, | 8,9,10,11,   | 16,17,18,19, | 24,25,26,27 |

|--------------------------------------|----------|--------------|--------------|-------------|

| <ul> <li>Slave: Timeslot</li> </ul>  | 4,5,6,7, | 12,13,14,15, | 20,21,22,23, | 28,29,30,31 |

The PCM Input/Output Interfaces are connected to the Speech Control Unit, Disabling Logic and the Microprocessor Interface.

#### 3.1.5 Subtractor

The subtractor calculates the difference between the signal from the PCM Send In Interface and the artificial echo provided by the Adaptive Echo Estimation Unit. The subtractor is controlled by the Speech Control.

#### 3.1.6 Non Linear Processor

The Non Linear Processor (NLP) limits the residual echo if only far end talk is present. Three programmable functions are available:

- Block echo and background noise.

- Replace echo and background noise by comfort noise with the level of the determined background noise.

- Clip the level of the echo and the background noise to the level of the background noise. (Experiments show that most people prefer this configuration)

The NLP is controlled by the Disabling Logic and Speech Control.

## 3.1.7 Microprocessor Interface

The Microprocessor Interface can operate in Intel and Motorola Mode. It provides access to the internal configuration, control states and monitor registers.

#### 3.1.8 Universal Control and Communication Interface

The UCC Interface is a serial hardware interface for SIDEC control and supervision by other boards via a Microprocessor. A special feature of the SIDEC-UCC Interface is, that

certain controlling functions like the channelwise disabling or  $A/\mu$ -Law conversion can be operated directly by the hardware without intervention of the microprocessor. This feature reduces the work load of the processor dramatically.

#### 3.1.9 Watchdog Timer

A Watchdog timer is implemented to reset the on board processor if the software gets stuck in an undefined state as a result of a faulty operation. A reset condition is met if the microprocessor fails to write predefined values to the three watchdog registers in the correct sequence within 2 s. As long as the watchdog is active the SIDEC generates interrupts and/or reset pulses of 125 µs width with a period of 2 s.

#### 3.1.10 Clock Control

The Clock Control supervises and generates all clock signals for proper operation of the ASIC hardware.

#### 3.1.11 JTAG and RAM BIST

The JTAG (Joint Test Application Group) has been implemented according to IEEE 1149.1. A RAM BIST (Random Access Memory Built In Self Test) is also provided.

## 3.1.12 Test

The Test Unit controls the background test on disabled channels. A built in self test is used for testing internal RAMs. This test can be activated after switching on the supply voltage. The test unit also supervises the Clock Control Unit.

A notebook register allows the check of the uP Interface.

Within the Test Unit the registers for background testing of idling channels are implemented. In this test a pattern is input in the idling channel at Receive in and Send in and evaluated at the Send out port.

During normal operation the Test Unit supervises functions such as read out of levels, internal states and coefficients.

# 3.2 Description of Functional Features

# 3.2.1 Channelwise and Global A- and μ-Law Conversion

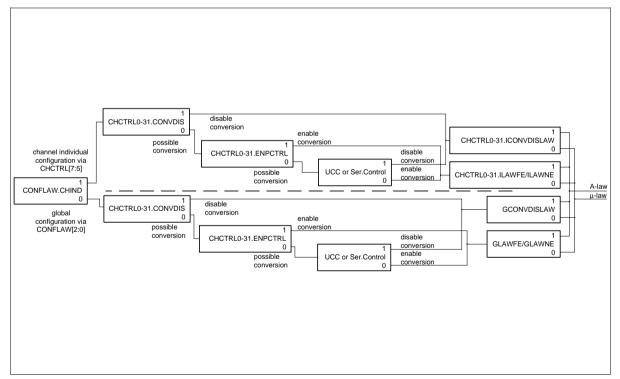

The SIDEC allows channel individual conversion. **Figure 8** depicts the implementation of the different options for the A- to  $\mu$ - or  $\mu$ - to A-Law conversion. Depending on the requirements of the application two settings can be configured: Either global or channel individual law conversion.

Global A- to  $\mu$  and  $\mu$  to A-Law conversion:

If this modus is chosen by setting CONFLAW.CHIND='0' all 32 PCM channels are converted according to the settings of GALAWFE for the far end and GALAWNE for the near end. A '1' in GALAWFE and GALAWNE indicates that A-Law is used for the corresponding end. A '0' indicates usage of μ-Law. The conversion can be disabled channel individually by setting the CHCTRL0-31.CONVDIS = '1' via software. Law decoding/encoding is then carried out according to GCONVDISLAW. To activate the serial control signal and the UCC interface as disabling source for the PCM law conversion the bits CHCTRL0-31.ENPCTRL must be set to '0'.

#### Channel individual A- to u- and u- to A-Law conversion:

For channel individual conversion the user can configure independently for each channel whether A- to  $\mu$ -,  $\mu$ - to A- or no Law conversion is selected via setting IALAWNE for the near end and IALAWFE for the far end with the corresponding value for A- or  $\mu$ -Law. The conversion can be disabled channel individually by setting the CHCTRL0-31.CONVDIS = '1' via software. Law decoding/encoding is then carried out according to CHCTRL0-31.CONVDISLAW. To activate the serial control signal and the UCC interface as disabling source for the PCM law conversion the bits CHCTRL0-31.ENPCTRL must be set to '0'.

Figure 8 Explanation of Options for A- and  $\mu$ -Law Conversion

## 3.2.2 Bypass and Disabling Functions

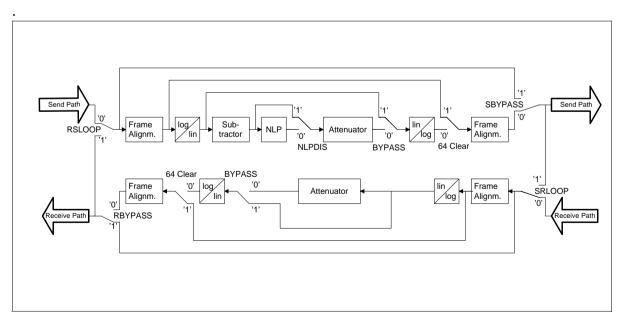

**Figure 9** depicts the bypass and disabling functions of the SIDEC. They can be configured via UCC, Serial and  $\mu P$  Interface.

Setting NLPDIS ='1' (pin or register setting) leads to bypassing of the Non Linear Processor.

Setting BYPASS = '1' (Serial control signal, UCC or 2100 Hz tone via register settings) results in bypassing the Attenuator in the Receive Path as well as in bypassing the Subtractor, the Non Linear Processor and the Attenuator in the Send Path.

Disabling a channel or the complete canceller will result in a BYPASS function, a H-Register reset and a reset of the Speech Control Unit. A bypassed or disabled channel of the SIDEC can still be converted from  $A/\mu$ - Law or vice versa.

If a Modem call is detected the user can define what action is related to the detection of a Modem call (2100 Hz with phase reversal or without reversal): bypassing, NLP bypassing, H-Register Reset or combination of the functions.

The 64 Clear mode is activated by bypassing and defining the same Law Conversion at near end and far end. In 64 Clear mode the signal is still passed through the frame alignment.

For testing purposes the canceller can be completly bypassed by setting SBYPASS and RBYPASS.

The Receive out signal can be input directly to the Send In port by setting the RSLOOP ='1'. The Send out signal can be input directly to the Receive in port by setting the SRLOOP ='1'. If both loops are configured only RSLOOP will be enabled in the SIDEC.

Figure 9 Bypass and Disabling Functions of the SIDEC

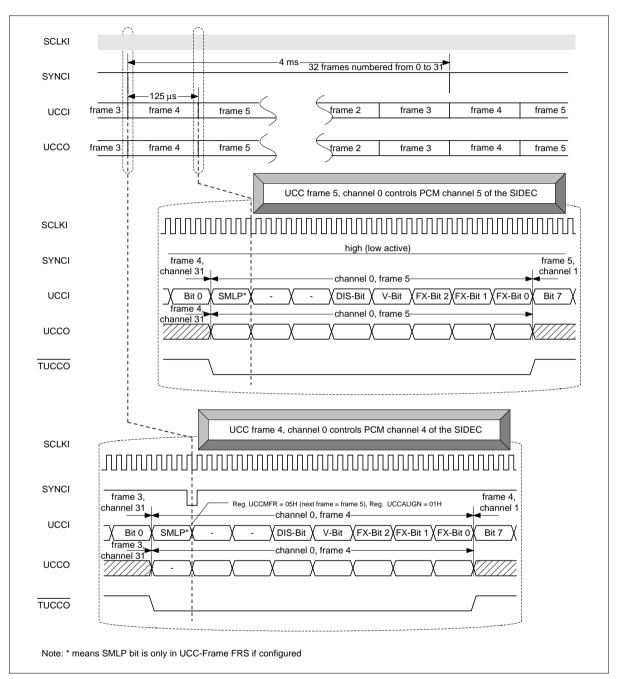

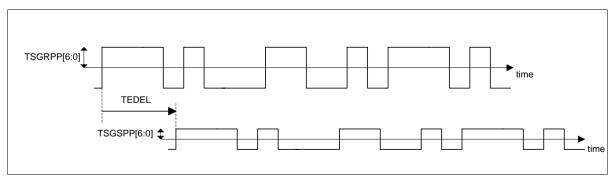

#### 3.2.3 UCC Interface

The UCC Interface uses a clock frequency of 2048 kHz. The UCC Signal is structured into frames (period 125  $\mu$ s) consisting of 32 channels (period 3.9  $\mu$ s) and a multiframe consisting of 32 frames (period 4 ms). The multiframe is synchronized with the SYNCI Input pulse. The SIDEC reads and writes (tristate controlled) only the channels 0 of the frames. The 32 channels 0 of each multiframe are used to control and supervise the associated PCM channels. UCC Frame 0 corresponds to PCM channel 0, UCC Frame 1 corresponds to PCM channel 1, .... This relation is depicted in **Figure 10**. It is also possible to use one special UCC-Frame for a general purpose. With the registers UCCMFR, UCCALIGN and PHALIGN[7:6] the UCC channel 0 of frame 0 can be shifted to any channel and frame. Hence, up to 32 different devices can be connected in parallel to the UCC Interface.

The output signal UCCO is always in phase with the UCCI input signal.

Figure 10 UCC Signal for control of PCM Signal

# 4 Operational Description

## 4.1 Pin Connection Diagram for SIDEC

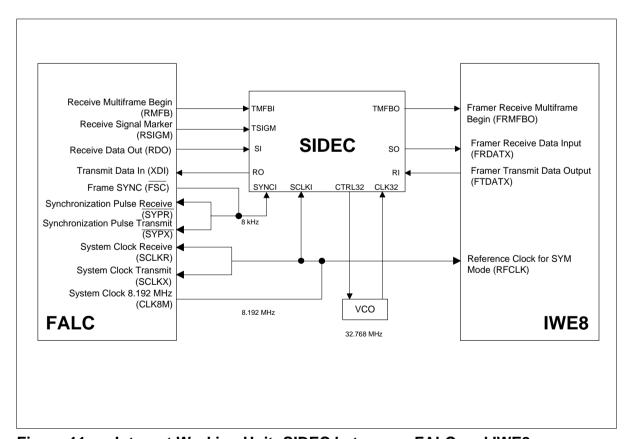

**Figure 11** illustrates an example for the pin connection of the SIDEC to an E1/T1 IC and to an interworking element IC.

The SIDEC is used to cancel the echo on the side of the FALC PEB 2254 or FALC-LH PEB 2255 which is the near end in this case. There are two SIEMENS products in this Inter working unit connected to the SIDEC. The FALC serves as a frame and line interface component whereas the IWE8 PEB 4220 operates as an interworking element. For multiframe alignment in the IWE8, FRMFBX must have a correct timing relation to FRDATX. For this purpose the SIDEC adjusts the delay from the TMFBI input to the TMFBO output to the delay of the SI input to the SO output. For the support of the CAS-BR transparency the SIDEC passes the robbed bits that are indicated by the FALC via the TSIGM input directly through to the SO output by overwriting the computed value of the robbed bit with the value of the SI input.

Figure 11 Internet Working Unit: SIDEC between a FALC and IWE8

### 4.2 Synchronization and Clock Modes

The SIDEC can be connected in different synchronization and clock modes. These modes can be used for several applications.

Basically there are two clock modes, slave and master clock mode (not to be mixed up with 128 ms master and slave mode). The internal clock system in master clock mode is automatically synchronized to the system clock by using an external 32.768 MHz VCO or by generating and deriving the system clock at output pin SCLKO directly from the CLK32 input. SIDEC in master clock mode provides a synchronization pulse at pin SDECO. This pulse can be used by a SIDEC in slave clock mode to synchronize its internal clock system to the system clock without the needs for additional external VCO.

Examples for this mode are the 128 ms delay application and the multiple SIDEC application, see also **Figure 16** and **Figure 17**.

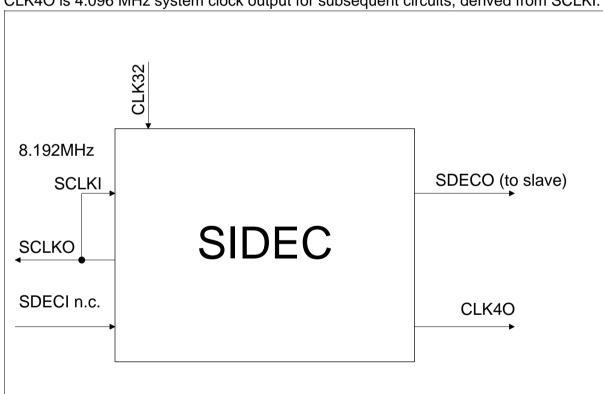

CLK4O is 4.096 MHz system clock output for subsequent circuits, derived from SCLKI.

Figure 12 Master Clock Mode with External 32.768 MHz Clock without 8.192 MHz System Clock Input

In **Figure 12** the system clock is reconnected from SCLKO to SCLKI in order to properly process the PCM signals. The system clock at pin SCLKO can also be provided for other devices. The SDECI pin is not connected in the master clock mode. A 32.768 MHz clock has to be provided by an external clock oscillator or other clock source on the system.

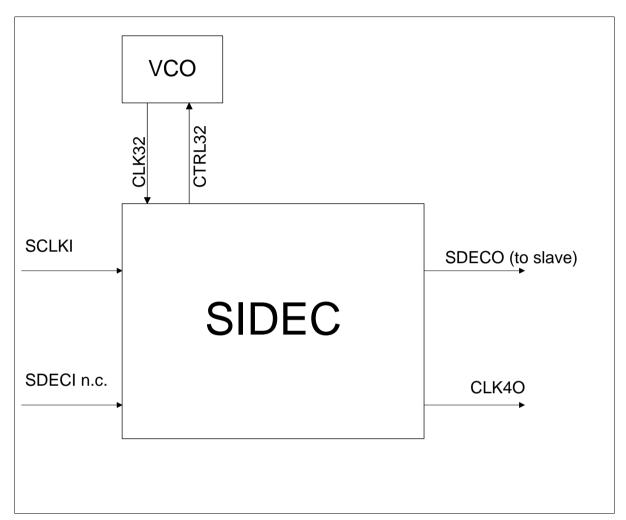

Figure 13 Master Clock Mode with External 8.192 MHz Clock

In the master clock mode with 8.192 MHz clock (**Figure 13**), the 32.768 MHz operating clock is supplied by the VCO. The SIDEC provides a controlling voltage for the VCO in order to synchronize the CLK32 to the system clock SCLKI.

SDECI is not connected and the SDECO can be connected to other SIDECs.

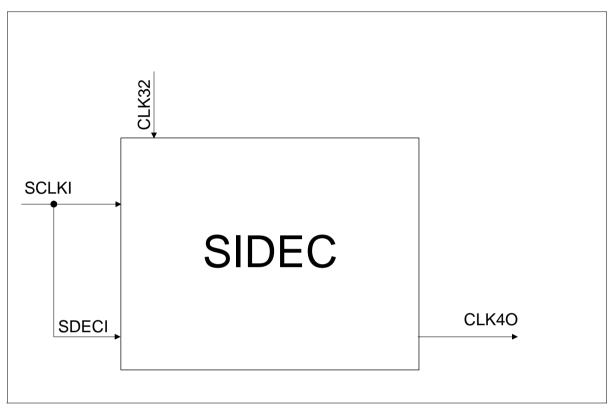

Figure 14 Slave Clock Mode with External 8.192 MHz and 32.768 MHz

In the slave clock mode the 8.192 MHz and the 32.768 MHz clock have to be synchronous and phase aligned (e.g. SCLKI has been derived from CLK32 by some external device). There is no internal synchronization between SCLKI and CLK32. SDECI is needed for correct phase alignment of SCLKI to the internal system clock.

CLK4O is a 4.096 MHz system clock output for subsequent circuits, derived from SCLKI

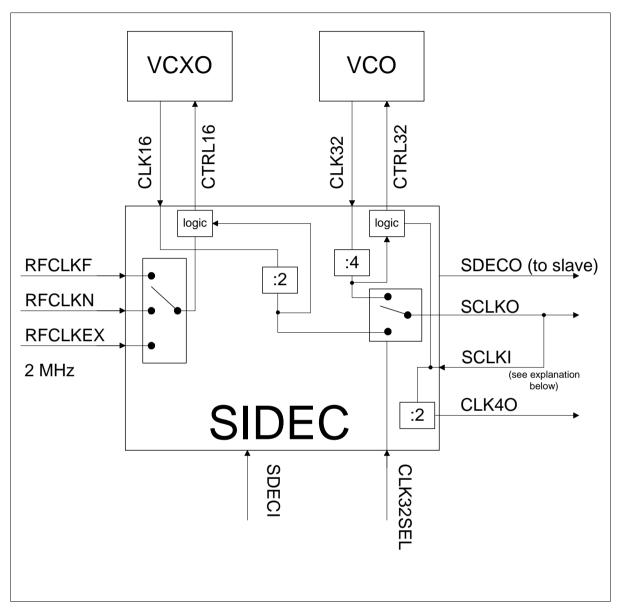

Figure 15 Reference Clock Mode with 2.048 MHz

In this mode a 2.048 MHz system clock is provided at either the RFCLKF, RFCLKN or the RFCLKEX pin. The VCXO and VCO supply the operating clocks for the SIDEC. SDECO can be connected to slave. The feedback from SCLKO to SCLKI in order to generate a control voltage for the 32 MHz VCO makes only sense if SCLKO is derived from CLK16. The SDECI initializes the counter.

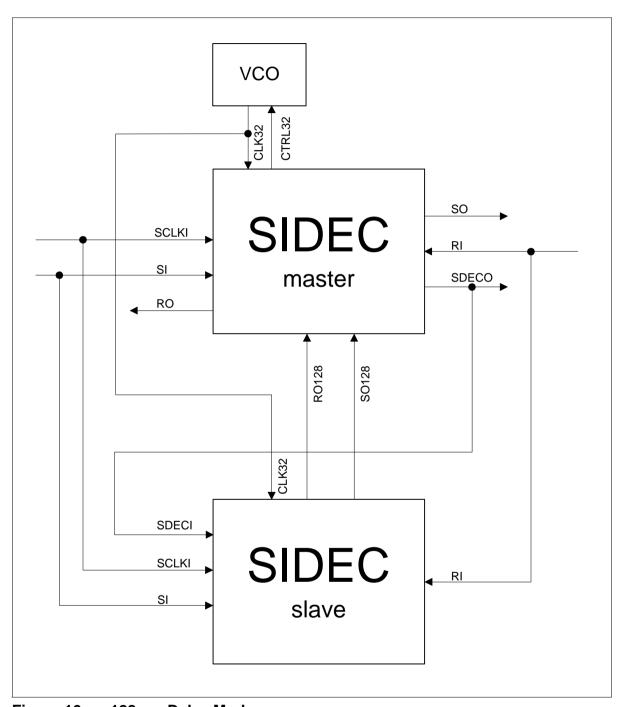

Figure 16 128 ms Delay Mode

The pin connection of a 128 ms master and slave SIDEC is shown in **Figure 16**. The SI and RI is supplied to both SIDECs. The RO and SO is provided by the master. The RO128 and SO128 signals are used to multiplex the 128 ms slave data into the PCM data stream outputs of the master.

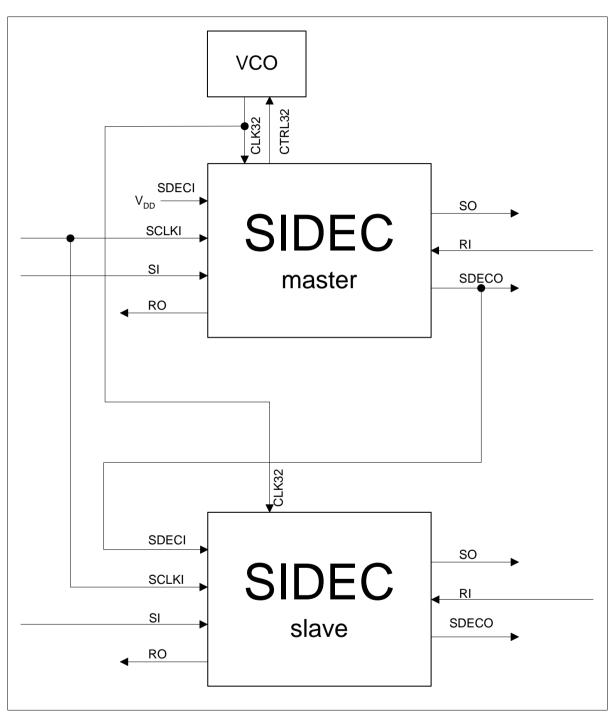

Figure 17 Multiple SIDEC

In multiple SIDEC mode the output SDECO of the clock master SIDEC is used to synchronize clock slave SIDECs to the system clock. In this application multiple E1/T1 lines can be echo cancelled, one E1/T1 line per SIDEC. Leave the SDECI of the master SIDEC open or connect it to ground.

# 4.3 Timing Patterns

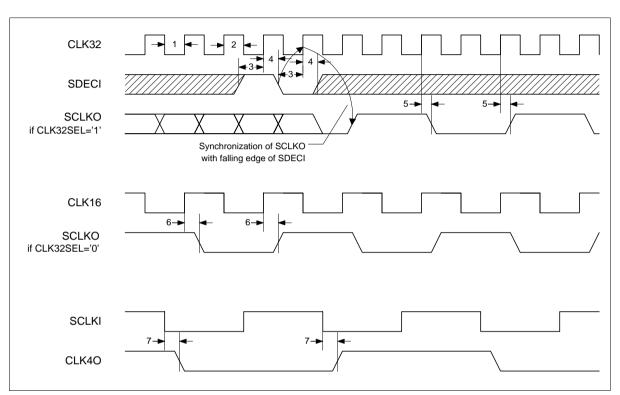

# 4.3.1 Clock Timing

Figure 18 Clock Timing

**Table 12** Clock Timing Characteristics (preliminary)

| No. | Name                | Parameter                        | Limit Values |      | Unit |

|-----|---------------------|----------------------------------|--------------|------|------|

|     |                     |                                  | min.         | max. |      |

| 1   | t_clk32_low         | CLK32 low time                   | 12           |      | ns   |

| 2   | t_clk32_high        | CLK32 high time                  | 12           |      | ns   |

| 3   | t_sdeci_setup       | SDECI setup time before CLK32 ↑  | 10           |      | ns   |

| 4   | t_sdeci_hold        | SDECI hold time after CLK 32 ↑   | 15           |      | ns   |

| 5   | t_sclko_delay_clk32 | SCLKO output delay after CLK32 ↑ |              | 30   | ns   |

| No. | Name                | Parameter                        | Limit Values |      | Unit |

|-----|---------------------|----------------------------------|--------------|------|------|

|     |                     |                                  | min.         | max. |      |

| 6   | t_sclko_delay_clk16 | SCLKO output delay after CLK16 ↑ | 0            | 30   | ns   |

| 7   | t_clk4o_delay       | CLK4O output delay after SCLKI ↓ | 0            | 30   | ns   |

# Table 13 Periods of Clock Signals

| No. | Parameter | min. | nom.   | Unit |

|-----|-----------|------|--------|------|

|     | CLK32     | 30   | 30.52  | ns   |

|     | CLK16     |      | 61.04  | ns   |

|     | SCLKI     |      | 122.07 | ns   |

|     | CLK4O     |      | 244.14 | ns   |

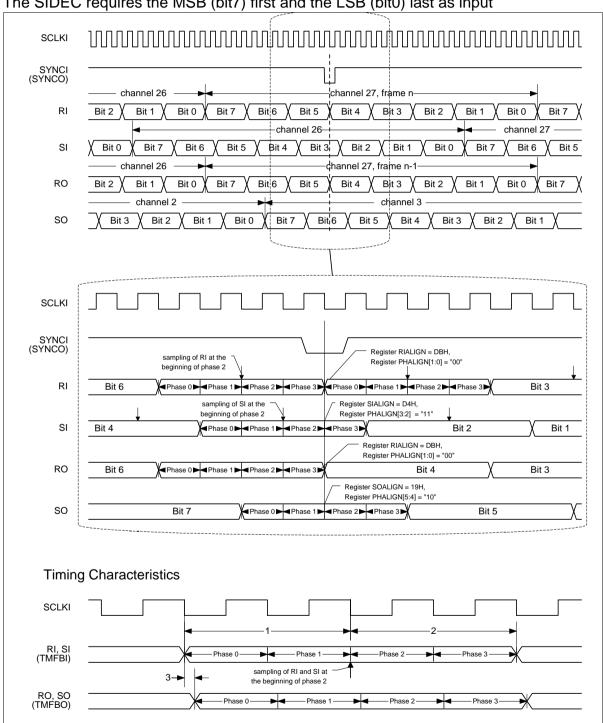

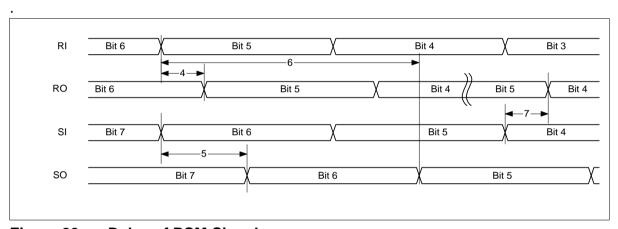

#### **PCM Signal Timing and Frame Alignment** 4.3.2

The SIDEC requires the MSB (bit7) first and the LSB (bit0) last as input

Figure 19 **PCM Signal Timing and Frame Alignment**

**Note:** Above values are examples only. PCM frame alignment with respect to the first detection of an active SYNCI (or SYNCO: If no SYNCI is applied, SYNCO takes over the part and role of SYNCI) with the falling edge of SCLKI can be configured by writing to the registers RIALIGN, SIALIGN an SOALIGN. For finer adjustments, the valid bit phase of the PCM signals at the first detection of an active SYNCI with the falling edge of SCLKI can be configured by writing to the register PHALIGN. The configured frame and bit phase alignment always denotes the beginning of the ideal bit phase (no signal delay) at the falling edge of SCLKI.

PCM inputs are always sampled with the falling edge of SCLKI at the beginning of bit phase 2, outputs are clocked with the falling edge of SCLKI at the beginning of bit phase 0. Unless not bypased the PCM output RO has a fixed delay of one PCM frame (125  $\mu$ s) with respect to RI.

Figure 20 Delay of PCM Signals

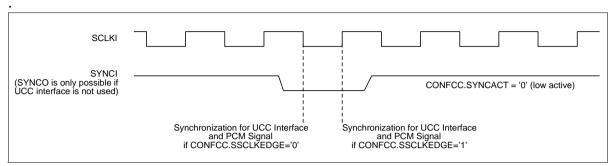

**Figure 21** illustrates the synchronization of the 2048 kBit/s PCM and UCC signal for a low active SYNCI signal with respect to the internal 8192 kHz SCLKI signal. If SYNCI is sampled with the falling edge of SCLKI (CONFCC.SSCLKEDGE='0') this edge is the synchronization point for PCM and UCC signals. If SYNCI is sampled with the rising edge of SCLKI (CONFCC.SSCLKEDGE='1') the next falling SCLKI edge is the synchronization point for PCM and UCC signals. The SYNCO signal may only be used instead of the SYNCI signal if the UCC Interface is not used

Figure 21 Synchronization of PCM and UCC Signal with respect to SCLKI and SYNCI

Table 14 PCM Signal Timing and Frame Characteristics (preliminary)

| No. |                   | Parameter                                                       | Lim  | Limit Values |    |

|-----|-------------------|-----------------------------------------------------------------|------|--------------|----|

|     |                   |                                                                 | min. | max.         |    |

| 1   | t_pcm_setup       | PCM input (RI,SI) input setup time before sampling with SCLKI ↓ | 15   |              | ns |

| 2   | t_pcm_hold        | PCM input (RI,SI) input hold time after sampling with SCLKI ↓   | 15   |              | ns |

| 3   | t_pcm_delay       | PCM output (RO,SO) delay after SCLKI ↓                          | 0    | 30           | ns |

| 4   | t_pcm_ri2ro_delay | delay for bypass RI to RO                                       | 0    | 30           | ns |

| 5   | t_pcm_si2so_delay | delay for bybass SI to SO                                       | 0    | 30           | ns |

| 6   | t_pcm_ri2so_delay | delay for bypass RI to SO                                       | 0    | 30           | ns |

| 7   | t_pcm_si2ro_delay | delay for bypass SI to RO                                       | 0    | 30           | ns |

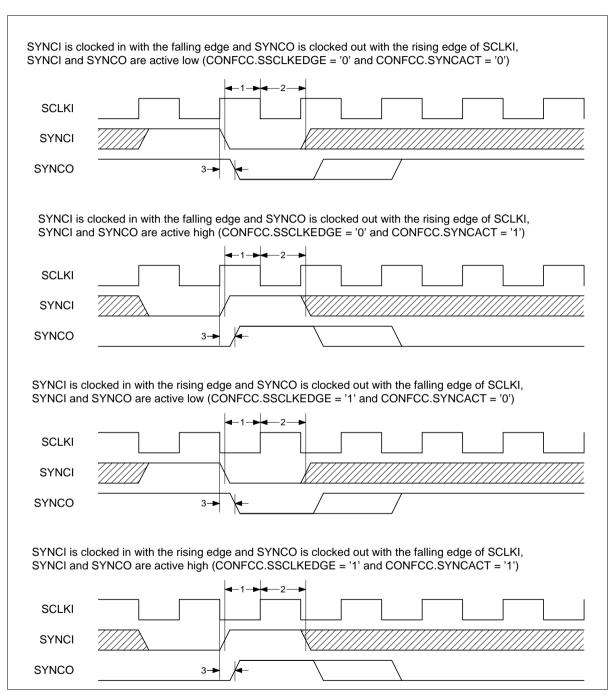

### 4.3.3 Timing of SYNCI and SYNCO

Figure 22 Timing of SYNCI and SYNCO

Figure 22 shows the timing of the synchronization pulses for different configurations.

**Note:** The duration of SYNCO pulse can be configured by register CONFCC.SYNCODUR to either one or two SCLKI (8.192 MHz) periods.

Table 15 Characteristics of Timing of SYNCI and SYNCO (preliminary)

| No. | Name          | Parameter                                                   | Limit Values |      | Unit |

|-----|---------------|-------------------------------------------------------------|--------------|------|------|

|     |               |                                                             | min.         | max. |      |

| 1   | t_synci_setup | SYNCI setup time<br>before active sampling<br>edge of SCLKI | 10           |      | ns   |

| 2   | t_synci_hold  | SYNCI hold time after active sampling edge of SCLKI         | 10           |      | ns   |

| 3   | t_synco_delay | SYNCO delay after active output edge of SCLKI               | 0            | 30   | ns   |

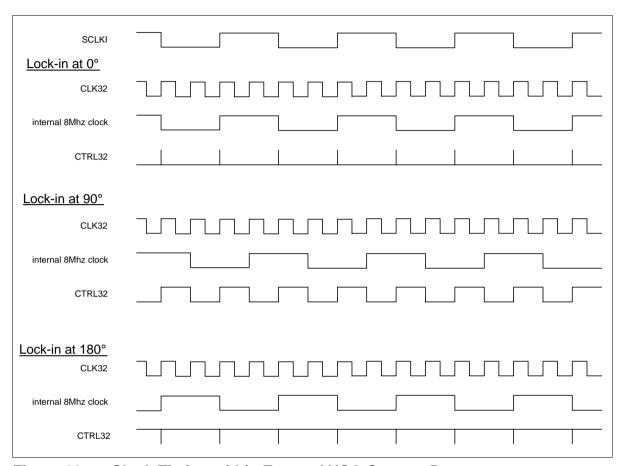

### 4.3.4 Clock Timing within External VCO Capture Range

Figure 23 Clock Timing within External VCO Capture Range

In case a 32.768 MHz clock has to be generated and synchronized to the system clock at SCLKI, the signal at pin CTRL32 can be used to control an external VCO. The output at CTRL32 is the signal at SCLKI that is internally 'xored' with an internal 8.192 MHz clock that is derived from the signal pin CLK32 by division by 4. For proper operation of the SIDEC the system clock SCLKI and the internal 8.192 MHz clock must lock in within the capture range from 0° to 180°. CTRL32 can be inverted by bit CONFCC.INVCTRL32 for use of VCOs that increase the frequency with falling voltage.

The internal 8.192 MHz clock can be monitored at pin SCLKO with a delay of three CLK32 periods plus internal signal delay if pin CLK32SEL is set to logic '1'.

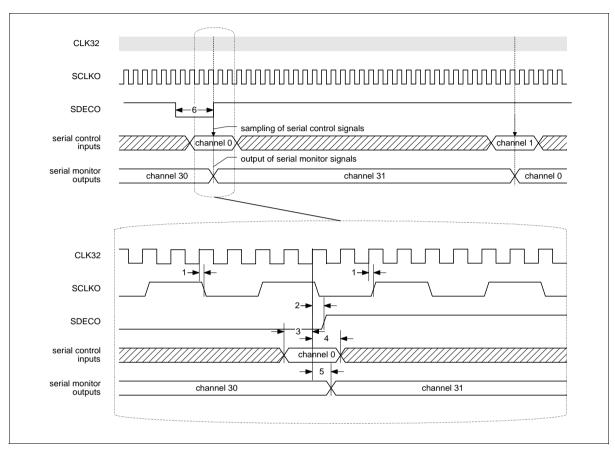

### 4.3.5 Serial Interface (Controlling and Monitoring) Timing

Figure 24 Serial Interface (Controlling and Monitoring) Timing

Table 16 Serial Interface (Controlling and Monitoring) Timing (preliminary)

| No. | Name          | Parameter                                                     | Limit Values |      | Unit |

|-----|---------------|---------------------------------------------------------------|--------------|------|------|

|     |               |                                                               | min.         | max. |      |

| 1   | t_sdeco_delay | SDECO output delay after CLK32 ↑                              | 0            | 30   | ns   |

| 2   | t_sctr_setup  | Serial control signal setup time before sampling with CLK32 ↑ | 15           |      | ns   |

| 3   | t_sctr_hold   | Serial control signal hold time after sampling with CLK32 ↑   | 15           |      | ns   |

| No. | Name         | Parameter                                        | Limit                   | Unit |    |

|-----|--------------|--------------------------------------------------|-------------------------|------|----|

|     |              |                                                  | min.                    | max. |    |

| 4   | t_smon_delay | Serial monitor signal output delay after CLK32 ↑ | 0                       | 30   | ns |

| 5   |              | SDECO duration                                   | 16 *<br>CLK32<br>period |      |    |

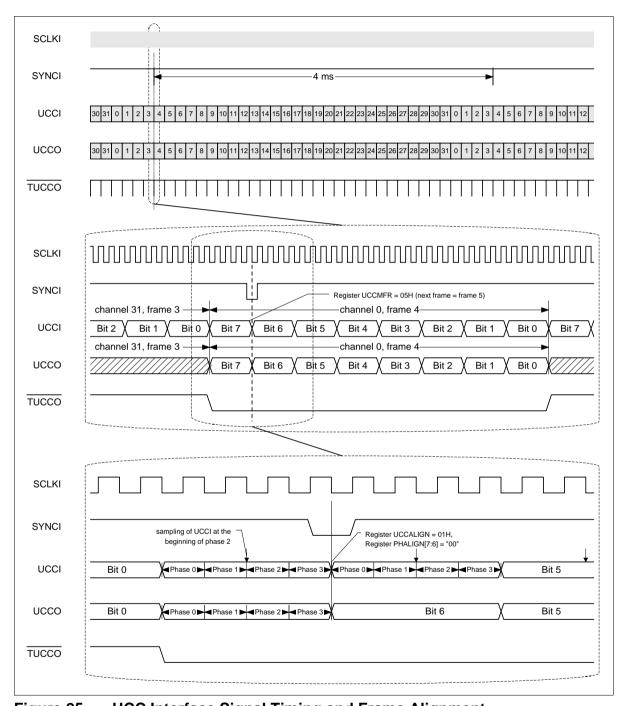

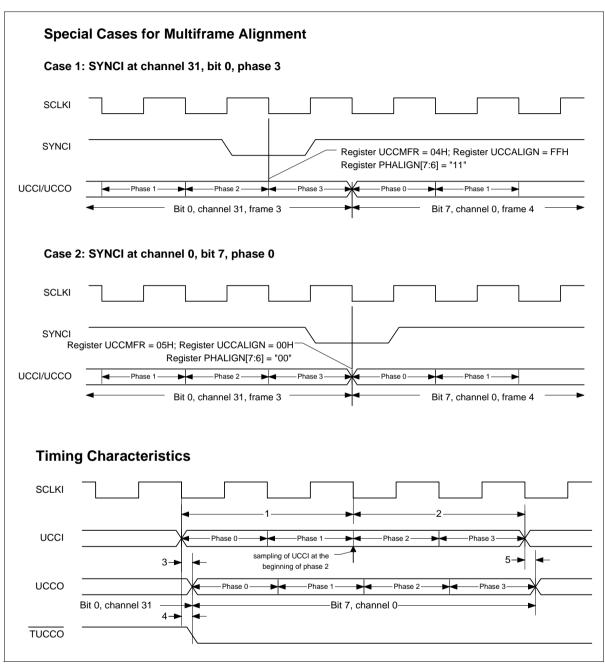

### 4.3.6 UCC Interface Signal Timing and Frame Alignment

Figure 25 UCC Interface Signal Timing and Frame Alignment

**Note:** Above values are examples only. For the use of the UCC Interface a SYNCI signal with a period of 4 ms (equivalent to one multiframe) must be applied to the SIDEC. UCC frame and multiframe alignment with respect to the first detection of an active SYNCI

with the falling edge of SCLKI can be configured by writing to the registers UCCALIGN and UCCMFR. For finer adjustments, the valid bit phase of the UCC signals at the first detection of an active SYNCI with the falling edge of SCLKI can be configured by writing to the two MSBs of register PHALIGN.

The configured frame and bit phase alignment always denotes the beginning of the ideal bit phase (no signal delay) at the falling edge of SCLKI. If SYNCI is sampled with the falling edge of SCLKI (CONFCC.SSCLKEDGE='0') this edge is the synchronization point for PCM and UCC signals. If SYNCI is sampled with the rising edge of SCLKI (CONFCC.SSCLKEDGE='1') the next falling SCLKI edge is the synchronization point for PCM and UCC signals. This behavior is identical to the PCM signal behavior and illustrated in **Figure 21** in **Chapter 4.3.2**

UCC inputs are always sampled with the falling edge of SCLKI at the beginning of bit phase 2, UCCO and TUCCO are clocked out with the falling edge of SCLKI at the beginning of bit phase 0. The value of register UCCMFR denotes the frame number of the next complete frame that starts with phase 0, bit 7, channel 0 **after** the first detection of an active SYNCI with the falling edge of SCLKI (see figure below).

Figure 26 Special Cases for Multiframe Alignment and Timing Characteristics

Table 17 UCC Interface Signal Timing and Frame Alignment (preliminary)

| No. | Name                | Parameter                                                | Limit | Values | Unit |

|-----|---------------------|----------------------------------------------------------|-------|--------|------|

|     |                     |                                                          | min.  | max.   |      |

| 1   | t_ucci_setup        | UCCI input setup time before sampling with SCLKI↓        | 15    |        | ns   |

| 2   | t_ucci_hold         | UCCI input hold time<br>after sampling with<br>SCLKI↓    | 15    |        | ns   |

| 3   | t_ucco_delay        | UCCO output delay<br>after SCLKI ↓                       | 0     | 30     | ns   |

| 4   | t_tucco_delay       | TUCCO output delay after SCLKI ↓                         | 0     | 30     | ns   |

| 5   | t_ucc_reflect_delay | Propagation delay from UCCI to UCCO for UCC reflect mode | 0     | 30     | ns   |

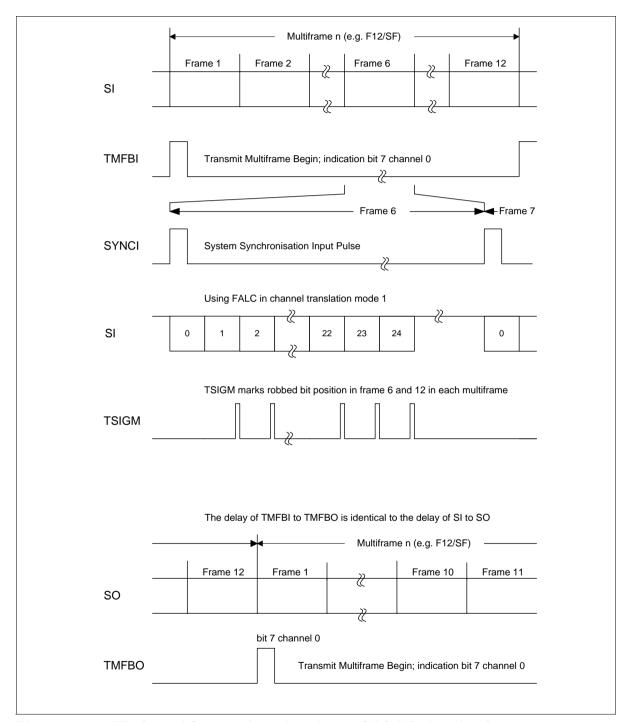

### 4.3.7 Speech Highway Control Signals for CAS in T1 Systems

Figure 27 Timing of Supporting signals for CAS-BR Applications

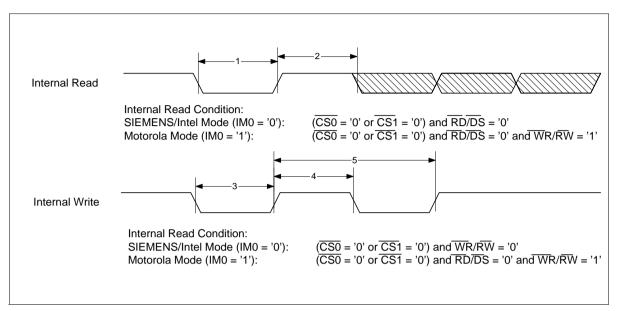

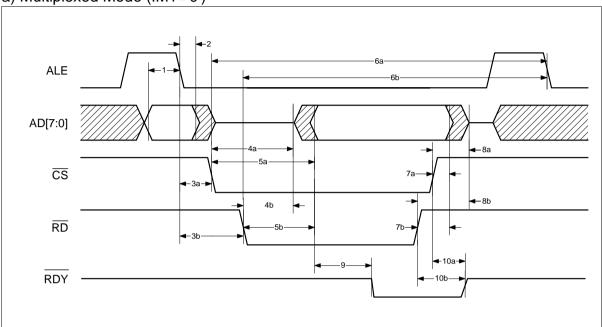

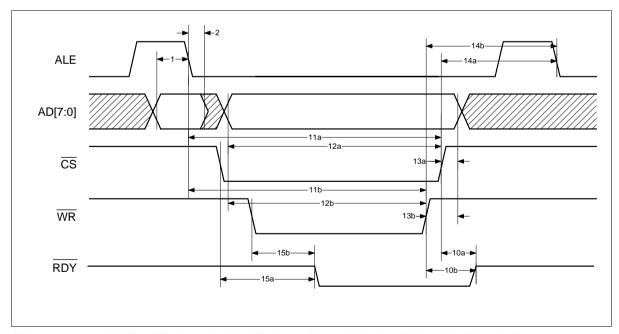

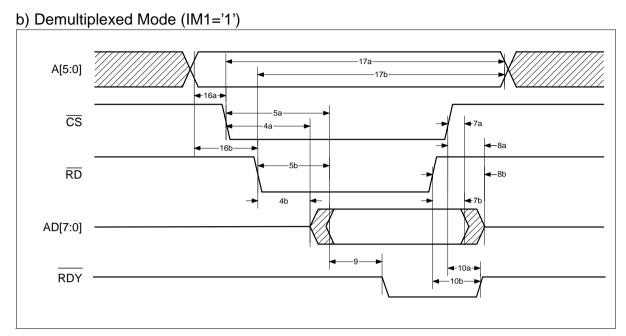

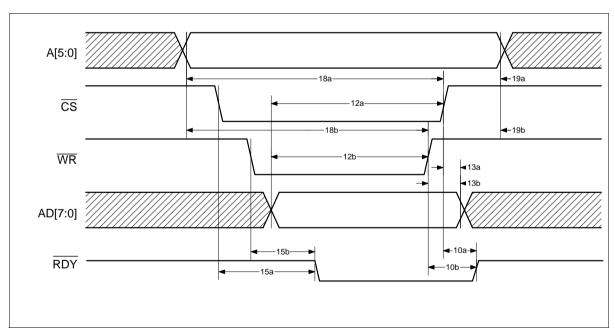

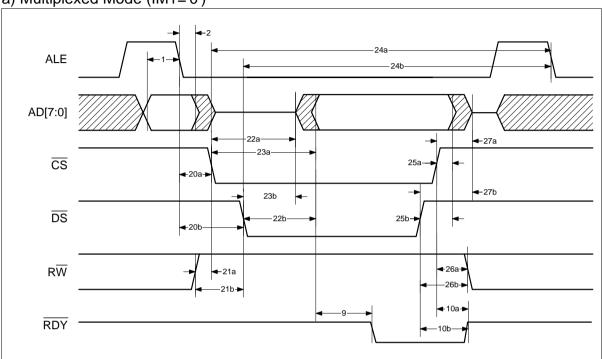

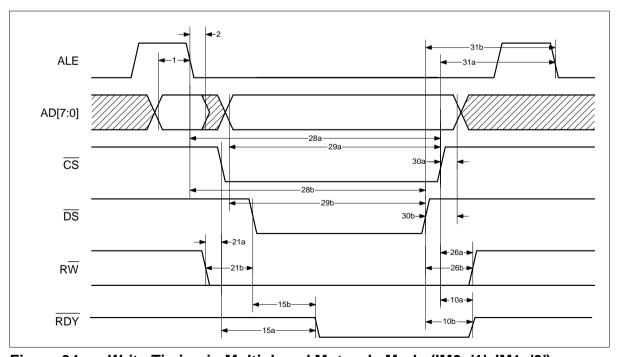

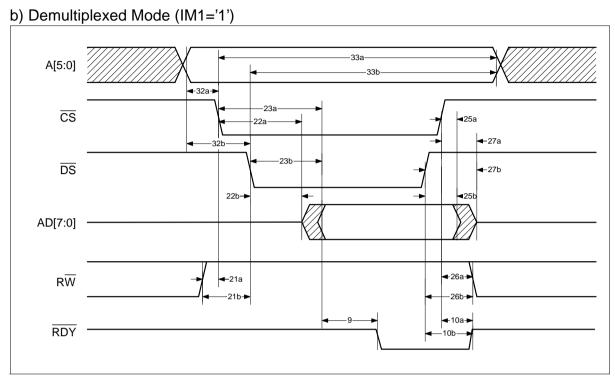

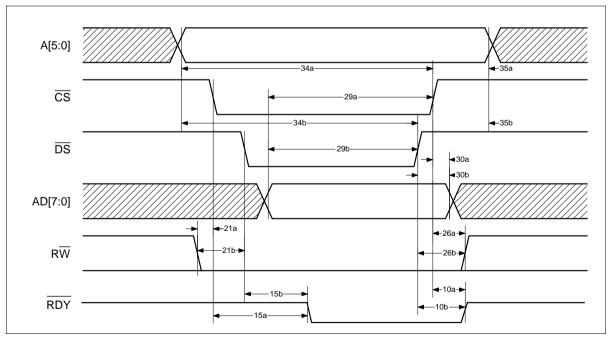

#### 4.3.8 Microprocessor Interface

The SIDEC Microprocessor Interface supports both, SIEMENS/Intel and Motorola mode. In each mode the address can be provided either through the multiplexed address/data or a parallel address bus. In multiplexed mode the address is always sampled with the falling edge of the address latch enable signal on the lower 7 bits of the multiplexed address/data bus. hence, adresses from 00H to 7FH are possible.

Read and write access in Intel mode is controlled by the assigned read and write signals. In Motorola mode it is provided by the data strobe and read/write signal.

The chip select signal is internally simply 'ored' with the read and write signal in Intel mode and with the data strobe signal in Motorola mode, thus enabling register access through chip select controlled Microprocessor cycles.

For fast processors there is also a ready/acknowledgment signal provided in order to eliminate the need for processor configured wait state insertion.

To write a value in a write protected register the value 95H needs to be written in the register Write Protection.

Figure 28 Internal Read Signal and Internal Write Signal

Table 18 Timing of (preliminary) Internal Read Signal and Internal Write Signal

| No. | Parameter                                      | Limit Values |      | Unit |

|-----|------------------------------------------------|--------------|------|------|

|     |                                                | min.         | max. |      |

| 1   | Active time                                    | 40           |      | ns   |

| 2   | Inactive time                                  | 40           |      | ns   |

| 3   | Active time                                    | 40           |      | ns   |

| 4   | Inactive time                                  | 40           |      | ns   |

| 5   | Interval between two active rising write edges | 120          |      | ns   |